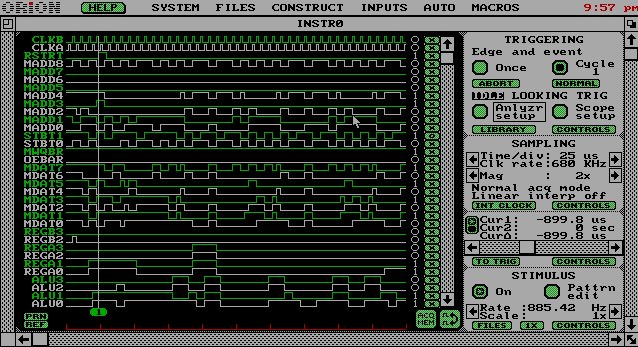

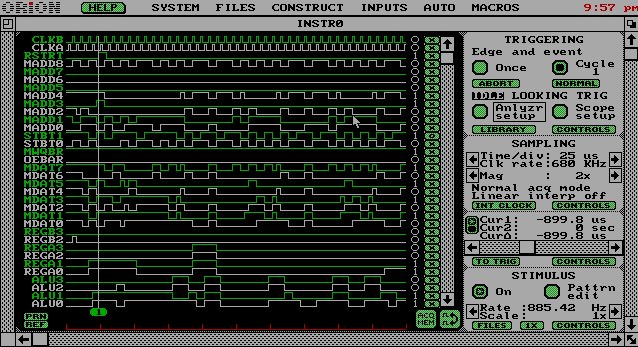

2nd Half of Results

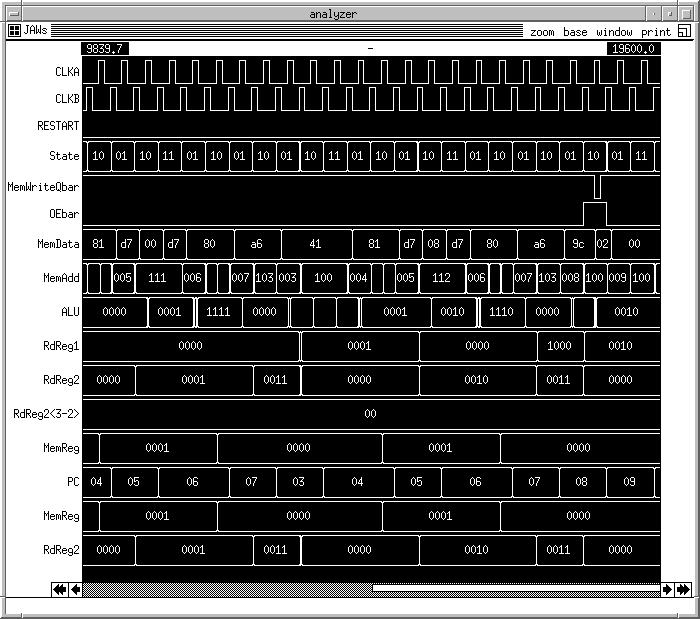

We check the correctness of our chips by observing the storing of the amount of sequential zeros in the array (which should be two). For more detailed verification we also compared the results of the program counter, instructions fetched, and register values with the expected values given by IRSIM.

Chips 2, 4, and 5 all passed this test with complete functionality.

Program Code: 0 LDI 0011 // reg3 gets the loop address 1 OR 1011 // reg2 gets the loop address 2 LWI 1111 // set reg3 to -1 loop: 3 SETMI 0001 // set the memory register 4 ADDI 0001 // increment reg3 5 LW 0111 // reg1 gets the next array element 6 SETMI 0000 7 BEZ 0110 // if reg1 is zero, then loop 8 SW 1100 // store the number of zeros at &0

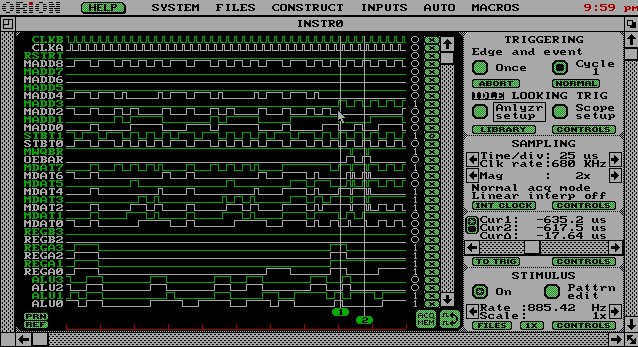

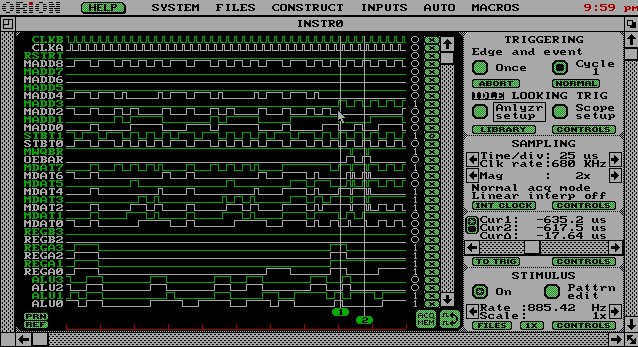

2nd Half of Results

2nd half of simulation

clock Vdd 1 1 1 1 clock CLKA 0 1 0 0 clock CLKB 0 0 0 1 | pin vectors vector MemData MemData7 MemData6 MemData5 MemData4 MemData3 MemData2 MemData1 MemData0 vector iMemData iMemData7 iMemData6 iMemData5 iMemData4 iMemData3 iMemData2 iMemData1 iMemData0 vector MemAdd MemAdd8 MemAdd7 MemAdd6 MemAdd5 MemAdd4 MemAdd3 MemAdd2 MemAdd1 MemAdd0 vector iMemAdd iMemAdd8 iMemAdd7 iMemAdd6 iMemAdd5 iMemAdd4 iMemAdd3 iMemAdd2 iMemAdd1 iMemAdd0 vector State StBit0 StBit1 vector RdReg1 RegA3 RegA2 RegA1 RegA0 vector RdReg232 RegB3 RegB2 vector ALU ALU3 ALU2 ALU1 ALU0 | pin ana's ana CLKA CLKB Restart MemAdd State MemWriteQbar OEbar MemData RdReg232 ana RdReg1 ALU Vdd ana Trigger ana ILOAD WE_L iMemData V RESTART 0 V iMemAdd 000000000 000000000 000000000 000000001 000000001 000000001 000000010 000000010 000000010 000000011 000000011 000000011 V ILOAD 0 V ILOAD_bar 1 V WE_L 1 0 1 1 0 1 1 0 1 1 0 1 V iMemData 11000011 11000011 11000011 00111011 00111011 00111011 11001111 11001111 11001111 10000001 10000001 10000001 R V iMemAdd 000000100 000000100 000000100 000000101 000000101 000000101 000000110 000000110 000000110 000000111 000000111 000000111 V iMemData 01000001 01000001 01000001 11010111 11010111 11010111 10000000 10000000 10000000 10100110 10100110 10100110 R V RESTART 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 V ILOAD 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 V ILOAD_bar 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 V WE_L 1 0 1 1 0 1 1 0 1 1 0 1 1 1 1 1 1 1 V iMemAdd 000001000 000001000 000001000 100010000 100010000 100010000 100010001 100010001 100010001 100010010 100010010 100010010 111111111 111111111 111111111 111111111 111111111 111111111 V iMemData 10011100 10011100 10011100 00000000 00000000 00000000 00000000 00000000 00000000 11111111 11111111 11111111 11111111 11111111 11111111 11111111 11111111 11111111 R V ILOAD 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 V ILOAD_bar 0 V WE_L 1 V iMemAdd 111111111 V iMemData 11111111 V RESTART 0 R