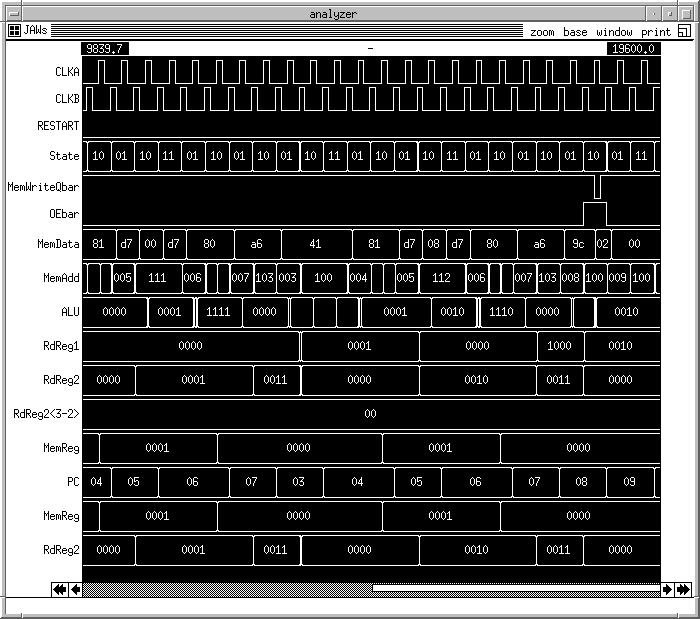

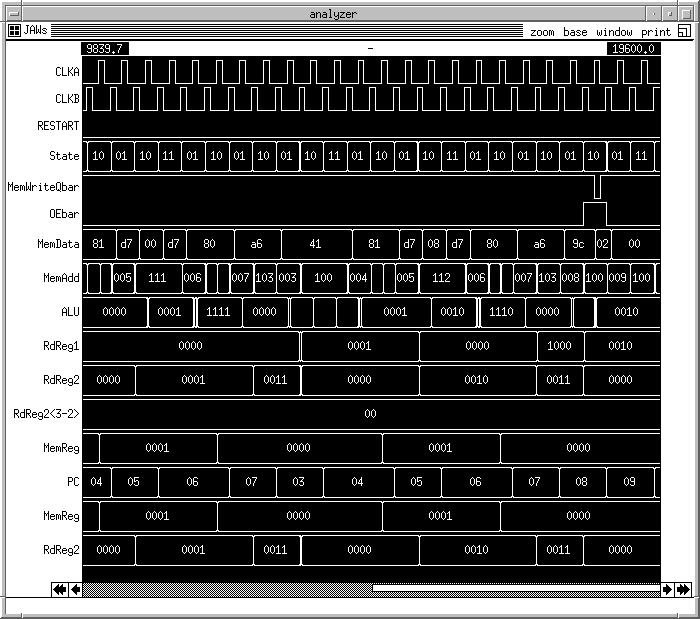

2nd half of simulation

Program Code: 0 LDI 0011 // reg3 gets the loop address 1 OR 1011 // reg2 gets the loop address 2 LWI 1111 // set reg3 to -1 loop: 3 SETMI 0001 // set the memory register 4 ADDI 0001 // increment reg3 5 LW 0111 // reg1 gets the next array element 6 SETMI 0000 7 BEZ 0110 // if reg1 is zero, then loop 8 SW 1100 // store the number of zeros at &0

2nd half of simulation

logfile cpu.log clock CLKA 0 1 0 0 clock CLKB 0 0 0 1 | pin vectors vector MemData MemData<7> MemData<6> MemData<5> MemData<4> MemData<3> MemData<2> MemData<1> MemData<0> vector MemAdd MemAdd<8> MemAdd<7> MemAdd<6> MemAdd<5> MemAdd<4> MemAdd<3> MemAdd<2> MemAdd<1> MemAdd<0> vector State StBit0 StBit1 vector RdReg1 RegA<3> RegA<2> RegA<1> RegA<0> vector RdReg2<3-2> RegB<3> RegB<2> vector ALU ALU<3> ALU<2> ALU<1> ALU<0> | core vectors vector PostMemData PostMemData<7> PostMemData<6> PostMemData<5> PostMemData<4> PostMemData<3> PostMemData<2> PostMemData<1> PostMemData<0> vector PC PC<7> PC<6> PC<5> PC<4> PC<3> PC<2> PC<1> PC<0> vector SelectedPC SelectedPC<7> SelectedPC<6> SelectedPC<5> SelectedPC<4> SelectedPC<3> SelectedPC<2> SelectedPC<1> SelectedPC<0> vector PCin PCin<7> PCin<6> PCin<5> PCin<4> PCin<3> PCin<2> PCin<1> PCin<0> vector PInF PInF<7> PInF<6> PInF<5> PInF<4> PInF<3> PInF<2> PInF<1> PInF<0> vector Add1in Add1in<7> Add1in<6> Add1in<5> Add1in<4> Add1in<3> Add1in<2> Add1in<1> Add1in<0> vector PAdd1 PAdd1<7> PAdd1<6> PAdd1<5> PAdd1<4> PAdd1<3> PAdd1<2> PAdd1<1> PAdd1<0> vector incPC incPC<7> incPC<6> incPC<5> incPC<4> incPC<3> incPC<2> incPC<1> incPC<0> vector PMRS PMRS<3> PMRS<2> PMRS<1> PMRS<0> vector MemReg RMDATA<3> RMDATA<2> RMDATA<1> RMDATA<0> vector intRegA intRegA<3> intRegA<2> intRegA<1> intRegA<0> vector RdReg2 intRegB<3> intRegB<2> intRegB<1> intRegB<0> vector PID PID<3> PID<2> PID<1> PID<0> vector PM2R PM2R<3> PM2R<2> PM2R<1> PM2R<0> vector MImm MImm<3> MImm<2> MImm<1> MImm<0> vector P4I P4I<3> P4I<2> P4I<1> P4I<0> vector PSrc2 PSrc2<3> PSrc2<2> PSrc2<1> PSrc2<0> vector PALU PALU<3> PALU<2> PALU<1> PALU<0> vector WBData WBData<3> WBData<2> WBData<1> WBData<0> vector PIR3 PIR3<1> PIR3<0> vector intState intStBit0 intStBit1 vector Ins Ins<7> Ins<6> Ins<5> Ins<4> Ins<3> Ins<2> Ins<1> Ins<0> | pin ana's ana CLKA CLKB Restart State MemWriteQbar OEbar MemData MemAdd ALU RdReg1 RdReg2 RdReg2<3-2> MemReg |ana intRestart |ana PostMemData |ana Ins |ana InF |ana intState |ana ClearRegs |ana ImpReg3 |ana FourImm |ana ALUSrc2 |ana RegWrite |ana Mem2Reg |ana ImmData |ana Branch |ana SetPC |ana RegRead |ana PCstore |ana PCstorebar ana PC |ana Add1in |ana EQZ GTZ |ana PBZ |ana PCSelect |ana PCin |ana PInF |ana PAdd1 |ana incPC |ana SelectedPC |ana PCin |ana PMRS ana MemReg |ana PALU |ana WBData |ana MImm |ana PM2R |ana PIR3 |ana intRegA ana RdReg2 |ana PID |ana PM2R |ana MImm |ana P4I |ana PSrc2 |ana PALU |ana WBData |ana PIR3 |ana Vdd |ana GND V RESTART 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 V MemData XXXXXXXX XXXXXXXX 11000011 11000011 00111011 00111011 00111011 11001111 11001111 10000001 10000001 01000001 01000001 01000001 1101 0111 00000000 11010111 10000000 10000000 10100110 10100110 01000001 01000001 01000001 10000001 10000001 11010111 00000000 11010111 10000000 100 00000 10100110 10100110 01000001 01000001 01000001 10000001 10000001 11010111 00001000 11010111 10000000 10000000 10100110 10100110 10011100 XX XXXXXX 00000000 00000000 R