This test is simple, yet effective. It verifies the bidirectionality of our MemData bus, as well as our chip's ability to read from and write to the SRAM. The result is verified when we read a value from memory immediately after writing it there. All data and addresses appear exactly as predicted.

Chips 2, 4, and 5 all passed this test with complete functionality. This program was also used as part of our speed test, since the write time to memory was believed to be our limiting factor in clock speed.

Program Code: 0 LDI 0101 // reg3 <= 0101 1 SW 1111 // Memory at Data address [00000101] <= $reg3 2 LW 0111 // reg1 <= Memory at Data address [00000101]

No irsim testing was performed for this test. It was created very recently, and due to its short length, we were easily able to predict the desired results ourselves.

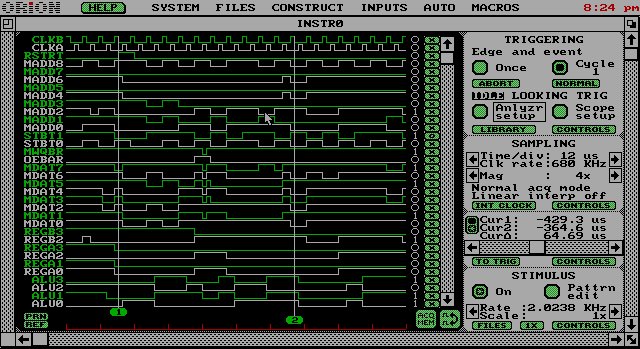

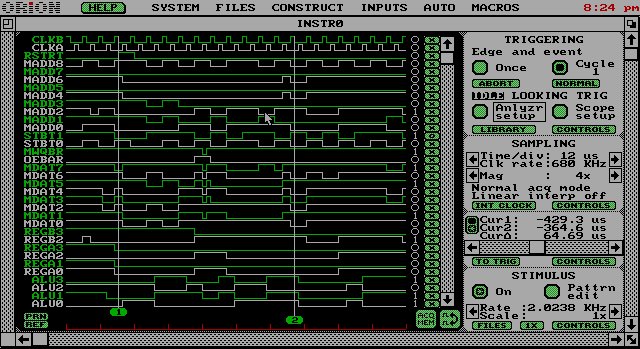

| SRAM Test logfile cpu.log clock Vdd 1 clock CLKA 0 1 0 0 clock CLKB 0 0 0 1 | pin vectors vector MemData MemData7 MemData6 MemData5 MemData4 MemData3 MemData2 MemData1 MemData0 vector iMemData iMemData7 iMemData6 iMemData5 iMemData4 iMemData3 iMemData2 iMemData1 iMemData0 vector MemAdd MemAdd8 MemAdd7 MemAdd6 MemAdd5 MemAdd4 MemAdd3 MemAdd2 MemAdd1 MemAdd0 vector iMemAdd iMemAdd8 iMemAdd7 iMemAdd6 iMemAdd5 iMemAdd4 iMemAdd3 iMemAdd2 iMemAdd1 iMemAdd0 vector State StBit0 StBit1 vector RdReg1 RegA3 RegA2 RegA1 RegA0 vector RdReg232 RegB3 RegB2 vector ALU ALU3 ALU2 ALU1 ALU0 | pin ana's ana CLKA CLKB Restart MemAdd State MemWriteQbar OEbar MemData RdReg232 ana RdReg1 ALU Vdd ana Trigger ana ILOAD WE_L iMemData |ana iMemAdd <- not enough room on analyzer pins V RESTART 0 0 0 0 0 0 0 0 0 0 0 1 V iMemAdd 000000000 000000000 000000000 000000001 000000001 000000001 000000010 000000010 000000010 111111111 111111111 111111111 V ILOAD 0 0 0 0 0 0 0 0 0 0 1 1 V ILOAD_bar 1 1 1 1 1 1 1 1 1 1 0 0 V WE_L 1 0 1 1 0 1 1 0 1 1 1 1 V iMemData 11000101 11000101 11000101 10011111 10011111 10011111 11010111 11010111 11010111 11111111 11111111 11111111 R V ILOAD 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 V ILOAD_bar 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 V WE_L 1 V iMemAdd 111111111 V iMemData 11111111 V RESTART 0 R