2nd half of simulation

This program multiplies the value at mem address 55 with the value at mem address AA, and it puts the result in mem address 00. In the test vectors below, the specific numbers to multiply are 3 and 2.

This program provides a good verification that JAWs can handle large programs with many branches. In the process, many ALU operations are performed, and the register file is accessed extensively. It was easy to verify a correct result; we look for a 6 to be written to memory at the end of the program. By also verifying the destination memory address, we have good assurance of the functionality of our chip. We also watched the PC throughout, making sure all appropriate branches are taken. We note that the SRAM always provides the expected instruction or data when requested.

Chips 2, 4, and 5 all passed this test with complete functionality. This program was also used as part of our speed test.

Program Code: 0 SETMI 1010 1 LDI 1010 2 LW 0011 // reg0 <= value at mem address AA 3 SETMI 0101 4 LDI 0101 5 LW 1011 // reg2 <= value at mem address 55 6 LDI 0001 7 SETMI 0001 8 BEZ 1011 // if $reg2 = 0, goto done 9 ZERO 0100 // reg1 <= 0 10 SETMI 0000 loop: 11 LDI 0001 12 SUB 1011 // decrement reg2 13 ADD 0100 // reg1 <= $reg1 + $reg0, reg1 is like an accumulator 14 LDI 1011 15 BGZ 1011 // if $reg2 is still greater than 0 loop done: 16 ZERO 1000 // reg2 <= 0 17 SW 0110 // store product at mem address 00

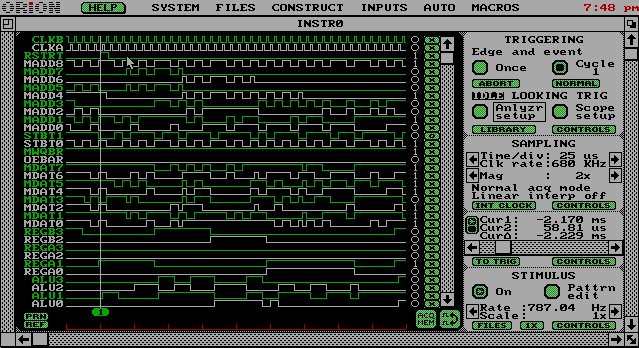

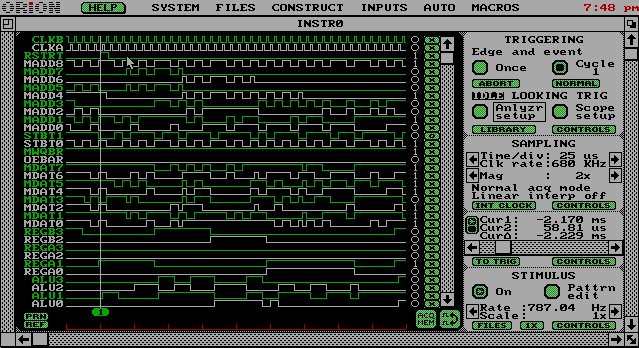

2nd half of simulation

2nd third of simulation

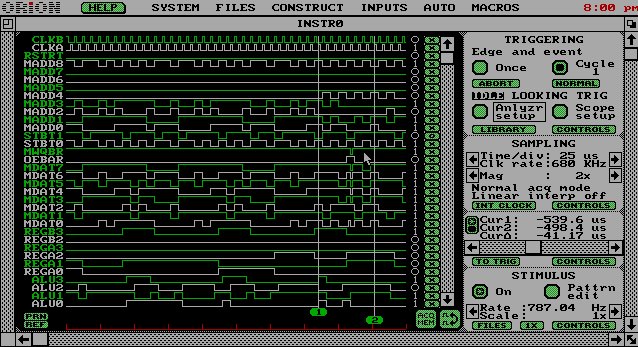

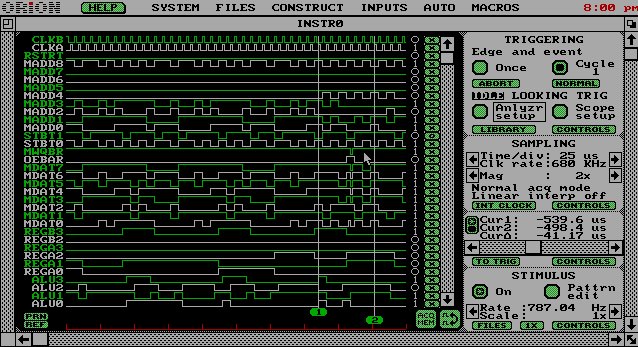

3rd third of simulation

| SRAM Test logfile cpu.log clock Vdd 1 1 1 1 clock CLKA 0 1 0 0 clock CLKB 0 0 0 1 | pin vectors vector MemData MemData7 MemData6 MemData5 MemData4 MemData3 MemData2 MemData1 MemData0 vector iMemData iMemData7 iMemData6 iMemData5 iMemData4 iMemData3 iMemData2 iMemData1 iMemData0 vector MemAdd MemAdd8 MemAdd7 MemAdd6 MemAdd5 MemAdd4 MemAdd3 MemAdd2 MemAdd1 MemAdd0 vector iMemAdd iMemAdd8 iMemAdd7 iMemAdd6 iMemAdd5 iMemAdd4 iMemAdd3 iMemAdd2 iMemAdd1 iMemAdd0 vector State StBit0 StBit1 vector RdReg1 RegA3 RegA2 RegA1 RegA0 vector RdReg232 RegB3 RegB2 vector ALU ALU3 ALU2 ALU1 ALU0 | pin ana's ana CLKA CLKB Restart MemAdd State MemWriteQbar OEbar MemData RdReg232 ana RdReg1 ALU Vdd ana Trigger ana ILOAD WE_L iMemData |ana iMemAdd <- not enough room on analyzer pins V RESTART 0 V iMemAdd 000000000 000000000 000000000 000000001 000000001 000000001 000000010 000000010 000000010 000000011 000000011 000000011 V ILOAD 0 V ILOAD_bar 1 V WE_L 1 0 1 1 0 1 1 0 1 1 0 1 V iMemData 10001010 10001010 10001010 11001010 11001010 11001010 11010011 11010011 11010011 10000101 10000101 10000101 R V iMemAdd 000000100 000000100 000000100 000000101 000000101 000000101 000000110 000000110 000000110 000000111 000000111 000000111 V iMemData 11000101 11000101 11000101 11011011 11011011 11011011 11000001 11000001 11000001 10000001 10000001 10000001 R V iMemAdd 000001000 000001000 000001000 000001001 000001001 000001001 000001010 000001010 000001010 000001011 000001011 000001011 V iMemData 10101011 10101011 10101011 11110100 11110100 11110100 10000000 10000000 10000000 11000001 11000001 11000001 R V iMemAdd 000001100 000001100 000001100 000001101 000001101 000001101 000001110 000001110 000001110 000001111 000001111 000001111 V iMemData 00011011 00011011 00011011 01010100 01010100 01010100 11001011 11001011 11001011 10111011 10111011 10111011 R V RESTART 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 V ILOAD 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 V ILOAD_bar 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 V WE_L 1 0 1 1 0 1 1 0 1 1 0 1 1 1 1 1 1 1 V iMemAdd 000010000 000010000 000010000 000010001 000010001 000010001 101010101 101010101 101010101 110101010 110101010 110101010 111111111 111111111 111111111 111111111 111111111 111111111 V iMemData 11111000 11111000 11111000 10010110 10010110 10010110 00000011 00000011 00000011 00000010 00000010 00000010 11111111 11111111 11111111 11111111 11111111 11111111 R V ILOAD 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 V ILOAD_bar 0 V WE_L 1 V iMemAdd 111111111 V iMemData 11111111 V RESTART 0 R